基于CPLD控制的高速数据采集板卡设计

在以个人计算机为核心的控制系统中,既需要把工业现场的模拟信号转换成计算机可以识别的数字信号、把计算机输出的数字信号转换成现场设备可接受的电压电流信号,又需要在某些要求高的场合实现高速数据交换。因此,高性能的32/6?位地址/数据复用局部总线PCI(外围部件互连)总线成为当今最流行的总线。

对高速数据采集系统而言,除了采用高速A/D转换器、高速存储器等高速器件之外,还要解决板卡如何高速寻址、如何控制总线逻辑、如何进行高速存储以及PC机如何读取数据等问题。

以前的数据采集板卡不带存储芯片,A/D芯片每转换出一个值,板卡就要和计算机通讯一次,以便将数据送入计算机,因此速率很低。本文介绍的PCI总线高速数据采集板卡设计,采用了简单易用的先进先出双口FIFO存储器,可以等A/D转换的数据存储到一定程度(例如FIFO半满)时才与计算机通讯一次,将数据送入计算机,从而大大节省计算机资源。

此外,该设计利用具有工作速度快、编程灵活优点的CPLD来实现板卡上各种逻辑控制。与以前采用很多逻辑元件完成所有时序控制的板卡相比,这样做可大大节省空间、降低成本。由于A/D芯片被完全解放出来,处于独立工作方式下,所以需要一个脉冲源来定时触发A/D转换。该设计直接将PCI总线上的33MHz的频率引出来,经CPLD的分频后触发A/D转换。

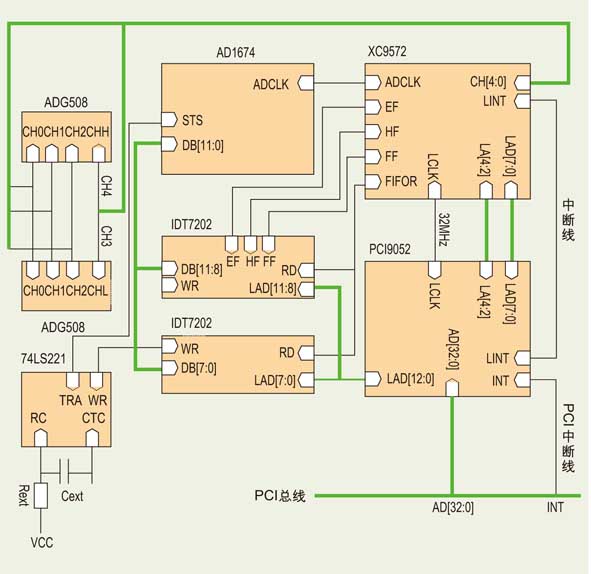

基于CPLD控制的高速数据采集板卡的硬件框图。

高速数据采集板卡采用了赛灵思公司的XC9572 CPLD芯片作为逻辑控制器,采用ADI公司的AD1674作为模数转换器(转换频率可达到100kHz,12位并行输出),FIFO存储器采用IDT公司的IDT7202,PCI接口芯片则采用PLX公司技术成熟、方便易用的PCI9052芯片。系统的硬件框图如图所示。

值得说明的是系统硬件框图中的连线都表示原理方面的连接,真正进行电气连接时要考虑信号间的匹配、时序等问题。

CPLD逻辑控制器的设计是高速数据采集卡的核心。按照前面所述的基本设计思想,整个数据采集板卡可以分为数据的转换存储以及数据传输两大部分。整个工作过程可以分为两个阶段完成:第一阶段是起动A/D转换,同时将转换的结果存入FIFO中,并对外部输入的多路电压信号进行通道转换;第二阶段是当FIFO达到半满时,板卡及时产生中断,通知计算机读数据,防止FIFO溢出而导致数据丢失。

第一阶段:CPLD给通道转换开关ADG508提供5个通道号信号线,如系统框图中的CH[4:0],其中CHH、CHL是两个ADG508的片选信号线,每个ADG508实现8路信号切换,两个可以实现16路的信号切换。

首先对CPLD编程实现采集通道的依次轮换,这部分程序见如下“通道切换VHDL代码”。从通道开关过来的电压信号经过运算放大器输送给处于独立工作方式的AD1674芯片。CPLD将直接从PCI总线引过来的33MHz频率进行分频后接到一个计数器模块,每来一个脉冲,计数值减一,减到零后输出一个脉冲触发该A/D芯片的一次转换过程。上位机可以设置计数器模块的时间常数,从而设置A/D转换频率。计数器模块的程序代码见如下的“计数器模块VHDL代码”。

A/D芯片每转换完一次,它的STS引脚变为低(转换时刻为高),这个信号触发FIFO写一次数据,将转换的数据锁入FIFO。但由于FIFO对触发写的低电平脉冲宽度有严格的要求,所以STS接到该FIFO之前要经过单稳态触发器74LS221。该触发器输出的低电平脉冲宽度可由公式tw(out)= 0.7* Cext *Rext确定。其中Cext和Rext分别为74LS221的外接电容和电阻。这样,A/D转换这一端的信号便被同步起来。读取FIFO数据的一端由PCI总线的时钟同步,并遵循严格的读写时序。

第二阶段:FIFO半满后,HF引脚就会变为低有效电平。这时,上位机要及时将FIFO中的数据读走,否则将有可能产生数据溢出,导致数据丢失。CPLD直接将FIFO的这个引脚接到总线芯片PCI9052的中断输入引脚,从而可以产生一个上位机中断,从而可在中断子程序中将数据一次性读出。每次中断视FIFO的容量而定,通常是容量的一半。我们在这个板卡设计中对FIFO部位使用了插座,只要将中断服务子程序中的读数据量作相应改动,使用者就可以方便地更换不同容量的FIFO。

当然,为使此板卡能有效工作,并充分发挥它的采集速度,还需要好的驱动程序和应用系统程序来有效处理传输过来的数据,这样才会使整个测控系统达到最优效果。

在需要采集多路模拟信号、数字信号的计算机测控系统中,利用CPLD芯片可以很好地将逻辑控制、数据信号处理等功能集于一身,从而有效提高系统的可靠性并降低系统实现成本。此外,利用功能强大的仿真软件工具,可以快速高效地完成CPLD的各种逻辑功能设计。

本文设计的基于CPLD控制的高速数据采集板卡充分利用了可编程逻辑控制器件的优点,完全达到了期望的控制功能。该板卡可在各种工控现场以及实验室条件下承担数据采集的任务,可广泛用于基于PC的控制系统。

附:通道切换VHDL代码entity fast_ch_DCD is port ( a3: in STD_LOGIC; ds: in STD_LOGIC; chh: out STD_LOGIC; chl: out STD_LOGIC );end fast_ch_DCD;

architecture fast_ch_DCD_arch of fast_ch_DCD isbegin process(a3,ds)-- <> BEGIN IF ds='0' THEN CASE a3 IS WHEN '0' =>chh<='1';chl<='0'; WHEN '1' =>chh<='0';chl<='1';

WHEN OTHERS =>chh<='0';chl<='1'; END CASE; ELSE chh<='1';chl<='1'; END IF;END PROCESS;

end fast_ch_DCD_arch;

‘高低控制entity sclo is port ( din:in STD_LOGIC_VECTOR(3 downto 0); CLK : in STD_LOGIC; load : in STD_LOGIC; QOUT : out STD_LOGIC_VECTOR(3 downto 0) );end sclo;

architecture inside of sclo is

signal qoutsig : STD_LOGIC_VECTOR(3 downto 0);

begin

process(CLK,load,din) begin

if(load='1') then qoutsig <=din; elsif(CLK'event and CLK='1') then --change "fi" to "if" if(qoutsig="0000") then qoutsig<=din; else qoutsig<=qoutsig - "0001"; end if; end if;

end process;

QOUT<=qoutsig;

end inside;

“计数器模块VHDL代码”代码

entity TIMECODE is Port ( din:in STD_LOGIC_VECTOR(9 downto 0); CLK : in STD_LOGIC; load : in STD_LOGIC; co:buffer STD_LOGIC );end TIMECODE;

architecture Behavioral of TIMECODE issignal qoutsig : STD_LOGIC_VECTOR(9 downto 0);signal tco:STD_LOGIC;beginprocess(CLK,load,din) begin

if(load='1') then qoutsig <=din;tco<='0'; elsif(CLK'event and CLK='1') then --change "fi" to "if" if(qoutsig="0000000000") then qoutsig<=din;tco<='1'; else qoutsig<=qoutsig - "0000000001";tco<='0'; end if; end if;

end process;process(tco,load) begin if (load='1') then co<='0'; elsif (tco'event and tco='1') then co<=not co; end if;

end process;

end Behavioral;

参考文献1、徐志军,徐光辉. CPLD/FPGA的开发与应用. 北京:电子工业出版社,20022、黄正谨,徐坚,章小丽.CPLD系统设计技术入门与应用. 北京:电子工业出版社,2002